## Corrections to the Text

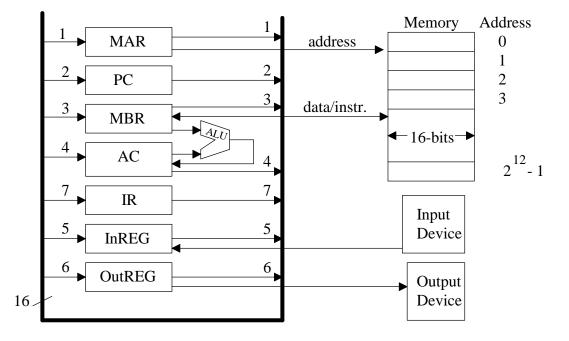

**In Figure 4.9** (the datapath in MARIE) it bothers me that the data into and out of the Main Memory comes from the Bus and not the MBR. I would prefer the following figure:

Revised Figure 4.9 Datapath in MARIE

Additionally, Figure 4.9 does NOT support the RTN of PC  $\leftarrow$  PC + 1, but that is a relatively minor issue.

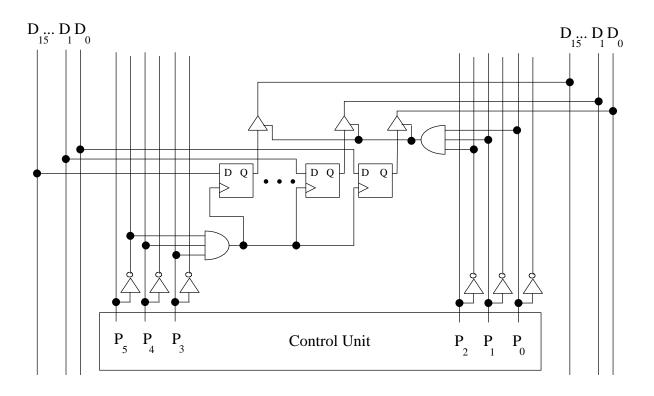

**Figure 4.15** seems to have numerous mistakes, especially related to connections of Flip-Flops to the Bus  $(D_{15}-D_0)$ . First, recall that seven registers are connected similarly to the Bus  $(D_{15}-D_0)$ . When the (upper) AND gates from the MBR register are outputting to the bus, the remaining registers would be outputting 0 to the same wires causing the values to be garbled. Similarly, when storing to a different register (other than the MBR), the D-input of the FFs will all be 0. Thus, clearing its contents. A revised Figure 4.15 is as follows:

Revised Figure 4.15 Connection of MARIE's MBR to Datapath

In Figure 4.14 (abc), the "(Decode IR[15-12])" occurs concurrently with the MAR  $\leftarrow$  IR[11-0], so I put "(Decode IR[15-12])" in the "Step" column instead of just "Decode". Additionally, I've added number to the steps in these table for later reference at the end of subsection 4.13.1.

| Step             | Step #                | RTN                     | PC  | IR   | MAR | MBR  | AC   |  |  |

|------------------|-----------------------|-------------------------|-----|------|-----|------|------|--|--|

| (initial values) |                       |                         | 100 |      |     |      |      |  |  |

| Fetch            | T <sub>0</sub>        | MAR ← PC                | 100 |      | 100 |      |      |  |  |

|                  | <b>T</b> <sub>1</sub> | MBR ← M[MAR]            | 100 |      | 100 | 1104 |      |  |  |

|                  | <b>T</b> <sub>2</sub> | IR ← MBR                | 100 | 1104 | 100 | 1104 |      |  |  |

|                  | <b>T</b> <sub>3</sub> | $PC \leftarrow PC + 1$  | 101 | 1104 | 100 | 1104 |      |  |  |

| Decode IR[15-12] | $T_4$                 | MAR ← IR[11-0]          | 101 | 1104 | 104 | 1104 |      |  |  |

| Get operand      | <b>T</b> <sub>5</sub> | $MBR \leftarrow M[MAR]$ | 101 | 1104 | 104 | 0023 |      |  |  |

| Execute          | <b>T</b> <sub>6</sub> | AC ← MBR                | 101 | 1104 | 104 | 0023 | 0023 |  |  |

## Revised Figure 4.14 (a) LOAD 104

## Revised Figure 4.14 (b) ADD 105

| Step                            | Step #                | RTN                      | РС  | IR   | MAR | MBR  | AC   |

|---------------------------------|-----------------------|--------------------------|-----|------|-----|------|------|

| (initial values AFTER LOAD 104) |                       |                          | 101 | 1104 | 104 | 0023 | 0023 |

| Fetch                           | T <sub>0</sub>        | MAR ← PC                 | 101 | 1104 | 101 | 0023 | 0023 |

|                                 | <b>T</b> <sub>1</sub> | $MBR \leftarrow M[MAR]$  | 101 | 1104 | 101 | 3105 | 0023 |

|                                 | $T_2$                 | IR ← MBR                 | 101 | 3105 | 101 | 3105 | 0023 |

|                                 | <b>T</b> <sub>3</sub> | $PC \leftarrow PC + 1$   | 102 | 3105 | 101 | 3105 | 0023 |

| Decode IR[15-12]                | $T_4$                 | MAR ← IR[11-0]           | 102 | 3105 | 105 | 3105 | 0023 |

| Get operand                     | <b>T</b> <sub>5</sub> | $MBR \leftarrow M[MAR]$  | 102 | 3105 | 105 | FFE9 | 0023 |

| Execute                         | T <sub>6</sub>        | $AC \leftarrow AC + MBR$ | 102 | 3105 | 105 | FFE9 | 000C |

## Revised Figure 4.14 (c) STORE 106

| Step                            | Step #                | RTN                     | PC  | IR   | MAR | MBR  | AC   |

|---------------------------------|-----------------------|-------------------------|-----|------|-----|------|------|

| (initial values AFTER LOAD 104) |                       |                         | 102 | 3105 | 105 | FFE9 | 000C |

| Fetch                           | <b>T</b> <sub>0</sub> | MAR ← PC                | 102 | 3105 | 102 | FFE9 | 000C |

|                                 | <b>T</b> <sub>1</sub> | $MBR \leftarrow M[MAR]$ | 102 | 3105 | 102 | 2106 | 000C |

|                                 | <b>T</b> <sub>2</sub> | IR ← MBR                | 102 | 2106 | 102 | 2106 | 000C |

|                                 | <b>T</b> <sub>3</sub> | $PC \leftarrow PC + 1$  | 103 | 2106 | 102 | 2106 | 000C |

| Decode IR[15-12]                | $T_4$                 | MAR ← IR[11-0]          | 103 | 2106 | 106 | 2106 | 000C |

| Execute*                        | <b>T</b> <sub>5</sub> | MBR ← AC                | 103 | 2106 | 106 | 000C | 000C |

|                                 | <b>T</b> <sub>6</sub> | $M[MAR] \leftarrow MBR$ | 103 | 2106 | 106 | 000C | 000C |

\* "Get Operand" step is not necessary for STORE instructions

On page 216 of the text, the "signal patterns" for the ADD RTN seem wrong in a number of ways:

- The timing signs used are T<sub>0</sub> T<sub>3</sub>, when using T<sub>4</sub> T<sub>6</sub> would make more sense since the "fetch" steps should be T<sub>0</sub> T<sub>3</sub>.

- "P<sub>0</sub> P<sub>2</sub> T<sub>1</sub>: MBR  $\leftarrow$  M[MAR]" should be "P<sub>4</sub> P<sub>3</sub> T<sub>5</sub>: MBR  $\leftarrow$  M[MAR]"

- For "AC ← AC + MBR", I'm not sure the P<sub>0</sub> and P<sub>1</sub> signals are needed since the AC and MBR are connected directly to the ALU. The P<sub>5</sub> signal makes some amount of sense if it triggers a "LOAD" of the AC.

The corrected signal patterns on page 216 should be:

P<sub>3</sub> P<sub>2</sub> P<sub>1</sub> P<sub>0</sub> T<sub>4</sub>: MAR  $\leftarrow$  IR[11-0] P<sub>4</sub> P<sub>3</sub> T<sub>5</sub>: MBR  $\leftarrow$  M[MAR] A<sub>0</sub> P<sub>5</sub> T<sub>6</sub>: AC  $\leftarrow$  AC + MBR C<sub>r</sub> T<sub>7</sub>: [Reset the clock cycle counter.]