HW #3 Computer Systems Solution

Due: 3/14/02 (Th)

1. The asynchronous Read timing diagram of Figure 3.19 bothers me. I think that the "slave" should not issue the SSYN and Data Line signals at the same time during the start of the Read.

a) Describe why this might create a problem.

When the slave asserts the SSYN at the same time as Data lines, the master might read the Data lines before they have stabilized. (I.e., because of bus skew, the SSYN might arrive at the master before all the Data signals.) If the master reads immediately when the SSYN is asserted, it could read garbage off the Data lines.

b) Propose a solution and draw a new timing diagram to fix this problem.

One solution would be to have the master wait sufficiently long after seeing that the SSYN is asserted before it reads the Data lines. In this solution, the figure does not need to be modified, but this solution seems a little inconsistent with the way the MSYN is handled.

An alternate solution would be for the slave to send the Data after it sees the MSYN is asserted. The slave can wait until the Data lines have stablized before asserting the SSYN line. The start of the figure would then look like:

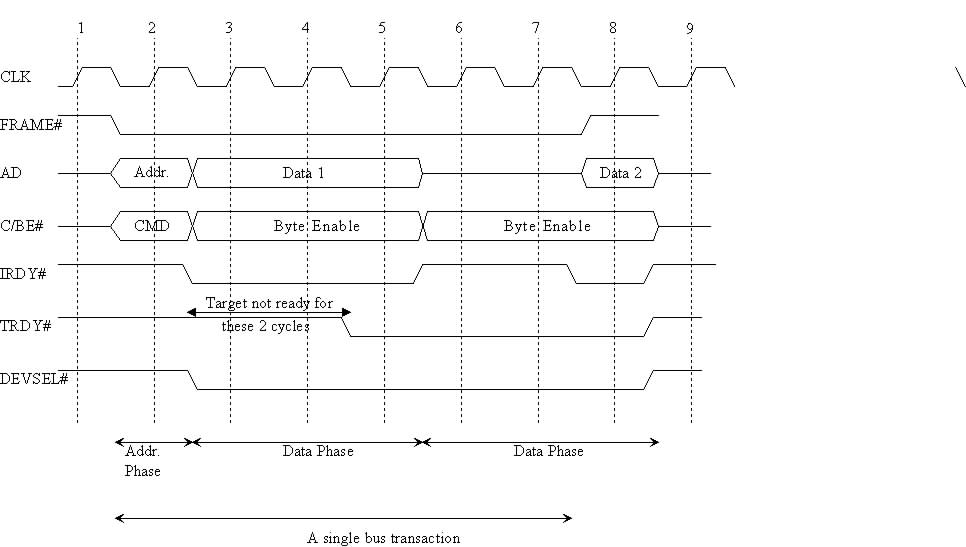

2. Draw and explain a timing diagram for a PCI write operation. Assume that 2 data transfers occur and that the following occurs during these transfers:

3. Draw and explain a timing diagram similar to Figure 3.24 assuming the followed: