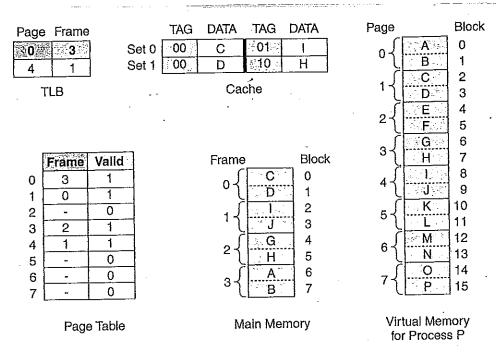

\*18. You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set associative cache, and a page table for a process P. Assume cache blocks of 8 bytes and page size of 16 bytes. In the system below, main memory is divided into blocks, where each block is represented by a letter. Two blocks equal one frame.

Given the system state as depicted above, answer the following questions:

- a) How many bits are in a virtual address for process P? Explain.

- b) How many bits are in a physical address? Explain.

- c) Show the address format for virtual address 18<sub>10</sub> (specify field name and size) that would be used by the system to translate to a physical address and then translate this virtual address into the corresponding physical address. (Hint: convert 18 to its binary equivalent and divide it into the appropriate fields.) Explain how these fields are used to translate to the corresponding physical address.

- d) Given virtual address  $6_{10}$  converts to physical address  $54_{10}$ . Show the format for a physical address (specify the field names and sizes) that is used to determine the cache location for this address. Explain how to use this format to determine where physical address 54 would be located in cache. (Hint: Convert 54 to binary and divide it into the appropriate fields.)

- e) Given virtual address 25<sub>10</sub> is located on virtual page 1, offset 9. Indicate exactly how this address would be translated to its corresponding physical address and how the data would be accessed. Include in your explanation how the TLB, the page table, cache, and memory are used.

- 19. Given a virtual memory system with a TLB, a cache, and a page table, assume the following:

- A TLB hit requires 5ns.

- A cache hit requires 12ns.

- A memory reference requires 25ns.

- A disk reference requires 200ms (this includes updating the page table, cache, and TLB).

- The TLB hit ratio is 90%.

- The cache hit rate is 98%.

- The page fault rate is .001%.

- On a TLB or cache miss, the time required for access includes a TLB and/or cache update, but the access is *not* restarted.

- On a page fault, the page is fetched from disk, all updates are performed, but the access is restarted.

- All references are sequential (no overlap, nothing done in parallel).

For each of the following, indicate whether or not it is possible. If it is possible, specify the time required for accessing the requested data.

- a) TLB hit, cache hit

- b) TLB miss, page table hit, cache hit

- c) TLB miss, page table hit, cache miss

- d) TLB miss, page table miss, cache hit

- e) TLB miss, page table miss

Write down the equation to calculate the effective access time.

20. A system implements a paged virtual address space for each process using a one-level page table. The maximum size of virtual address space is 16MB. The page table for the running process includes the following valid entries (the → notation indicates that a virtual page maps to the given page frame, that is, it is located in that frame):

Virtual page  $2 \rightarrow$  Page frame 4

Virtual page 4 → Page frame 9

Virtual page  $1 \rightarrow \text{Page frame } 2$

Virtual page 3 → Page frame 16

Virtual page  $0 \rightarrow \text{Page frame } 1$

The page size is 1024 bytes and the maximum physical memory size of the machine is 2MB.

- a) How many bits are required for each virtual address?

- b) How many bits are required for each physical address?

- c) What is the maximum number of entries in a page table?

- d) To which physical address will the virtual address 1524<sub>10</sub> translate?

- e) Which virtual address will translate to physical address 1024<sub>10</sub>?